Preliminary Schedule

8:30–8:40 |

Welcome Remarks |

General Architectures (8:40 AM – 10:00 AM)

|

|

8:40–9:00 |

Securing the Processor-to-Processor and Processor-to-Memory Communication Links [Paper] [Presentation]

|

9:00–9:20 |

Temperature and Process Variation-Aware Wavelength Selection in Photonic NoCs [Paper] [Presentation]

|

9:20–9:40 |

Hardware-Software Coordination for High Performance Concurrent Data Structures with Near-Data-Processing [Paper] [Presentation]

|

9:40–10:00 |

GPU Architecture Optimization for Mobile Computing

|

Coffee Break (10:00 AM–10:15 AM)

|

|

Security (10:20 AM–11:20 AM)

|

|

10:20–10:40 |

Designing a Secure DRAM+NVM Hybrid Memory Module [Paper] [Presentation]

|

10:40–11:00 |

Can We Reliably Detect Malware Using Hardware Performance Counters? [Paper] [Presentation]

|

11:00–11:20 |

CodeTrolley: Hardware-Assisted Control Flow Obfuscation [Paper] [Presentation]

|

Designs around RISC-V (11:20 AM–12:00 PM)

|

|

11:20–11:40 |

Formally Verifying Many RISC-V Implementations with One Page of Code [Paper] [Presentation]

|

11:40–12:00 |

Hardware Assisted Transparent ROP Mitigation for RISC-V

|

Lunch Hour (12:00 PM–1:00 PM)

|

|

1:10–1:40 |

Cryptographically Attested Secure Hardware for Enclaves [Presentation]

|

1:40–2:00 |

Tools for RISC-V Design Space Exploration

|

Machine Learning Acceleration (2:00 PM–3:00 PM)

|

|

2:00–2:20 |

Dynamic Precision Tunability in Low-Power Training of Deep Neural Networks [Paper] [Presentation]

|

2:20–2:40 |

Evaluation of Volta-based DGX-1 System Using DNN Workloads [Paper] [Presentation]

|

Coffee Break (2:40 PM–2:55 PM)

|

|

Invited Speaker (3:00 PM–3:40 PM)

|

|

|

The Vision Behind MLPerf (mlperf.org): A Community-driven ML Benchmark Suite for Software Frameworks and Hardware Accelerators in Cloud and Edge Computing

|

|

Quantum and Post-Quantum Computing (3:40 PM–4:40 PM)

|

|

3:40–4:00 |

A Lightweight McEliece Cryptosystem Co-Processor Design [Paper]

|

4:00–4:20 |

Delegating Quantum Computation Using Only Hash Functions

|

4:20–4:40 |

Ring-Learning with Errors Post-Quantum Cryptographic Hardware Primitives [Paper]

|

4:40–4:50 |

Closing Remarks |

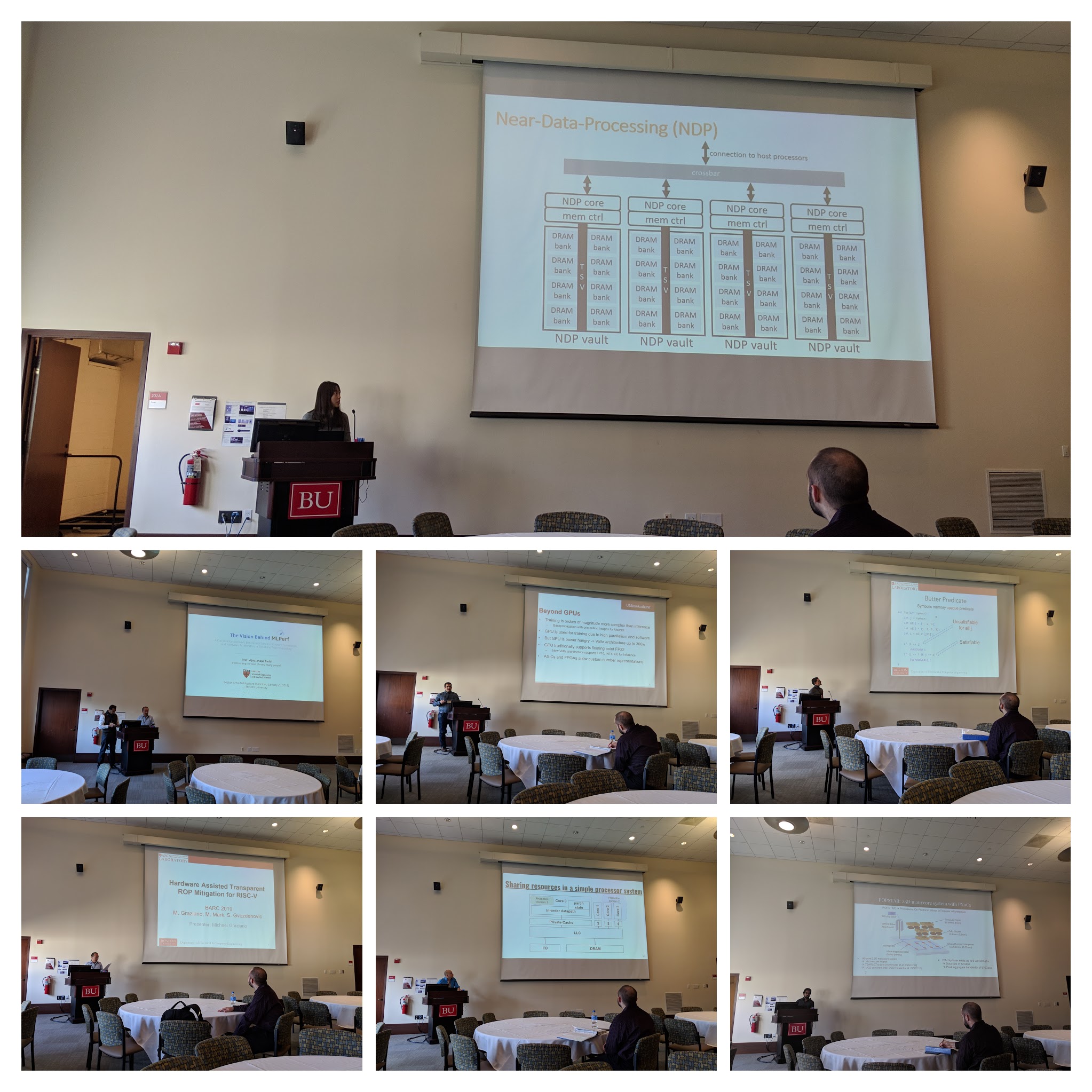

Pictures from the workshop!

Registration

- Industry participants: $50

- Academic participants - faculty: $50

- Academic participants - student: FREE (Student registrations must be sponsored by a faculty member).

The registration is now open. Link here.

Registration includes breakfast, light lunch, and coffee during all breaks.Call for Abstracts

Scope:

The goal of BARC is to provide a forum for computer architects in the Greater Boston area and beyond to get together and present/discuss the “latest and greatest” in the area of computer architecture. Papers are being sought on all aspects of computer architecture, including (but not limited to):

Important Dates:

Abstract Submission Deadline: January 7, 2019

Author Notification: January 14, 2019

Workshop Date: Friday, January 25, 2019

Submissions:

We invite abstracts, two pages or shorter, for consideration for presentation at BARC 2019. Authors may present work they have already published elsewhere, or plan to publish in the future. We welcome participation from those outside of the Greater Boston area.

Please submit your abstract (in PDF format) using EasyChair:

https://easychair.org/conferences/?conf=barc19.

Abstracts will be accepted for a regular podium presentation or for a poster presentation. All accepted abstracts will be published in the workshop proceedings.

Call for Abstracts in [PDF]

Example Latex templates can be found [HERE].

For questions, contact Michel A. Kinsy or

Ajay Joshi.

- Manuscript should be two-pages long.

- Text should use two column format.

- One-inch margin should be left on all sides.

- Using at least a 10-pt font is recommended.

- Submissions should be in PDF format.

Directions

BARC 2019 will be held at the BU Wheelock College Brookline Campus, Second Floor - Ladd Room. The full address is 43 Hawes St, Brookline, MA 02446.